**Reed Business Information (RBI**)

VOICE OF THE ENGINEER

Dark side of the light Pg 58

EDN.comment: Selfserving "synergy" Pg 5

**Signal Integrity:** The nature of ESD Pg 10

Design Ideas Pg 43

Supply Chain Pg 54

Product Roundup Pg 56

## SPEAKING OF PORTING SOFTWARE

117

Issue 15/2009 www.edn.com

> AMBIENT-LIGHT SENSORS PACK IN FEATURES TO HELP APPLICATIONS GET SMARTER, GREENER Page 13

IMS HIGHLIGHTS STUDENT INGENUITY Page 25

TECHNIQUES FOR IMPLEMENTING HIGH-PERFORMANCE PROCESSOR CORES Page 28

DRAM TECHNOLOGY FOR SOC DESIGNERS AND—MAYBE— THEIR CUSTOMERS Page 34

FIRST-PASS SUCCESS IN SILICON PACKAGING Page 38

Intelligent Light Solutions from NEC Electronics America www.am.necel.com/led

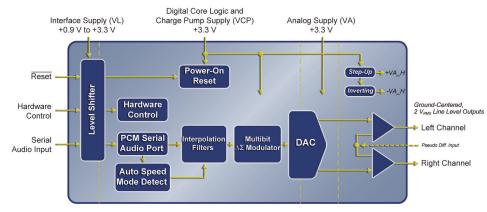

The CS4353 Is Based on a Charge-Pump Architecture and Features an On-Chip 2 V<sub>RMS</sub> Line Driver Working from a Single 3.3 V Power Supply Without the Need for a High Voltage Regulator. Also a Ground-Centered Output Removes the Need for External DC Blocking Capacitors and Any Pop Prevention Circuit.

### Finally—A No Compromises Digital-to-Analog Converter

Cut the clutter! When it comes to digital-to-analog converters, Cirrus Logic means business. The CS4353 is the only audio DAC to feature an on-chip 2.1  $V_{RMS}$  line driver from a single 3.3 V power supply, allowing a 2  $V_{RMS}$  voltage after the RC filter. The new architecture not only simplifies the design of analog output section circuitry but it also provides superior quality audio playback with the highest dynamic range and lowest pops and clicks of its kind. This is especially important in applications such as Blu-ray Disc<sup>®</sup> players, DTV and set-top boxes as they allow for the elimination of multiple system components and lower implementation cost.

CS4353 FEATURES

- 106 dB dynamic range, -93 dB THD+N

- Single-ended ground centered analog architecture

- No DC-blocking capacitors required

- Click-free stereo output

- Selectable 1 or 2 V<sub>RMS</sub> full-scale output

- High PSRR

- Small 4 mm x 4 mm QFN package

Cirrus Logic. We make it easier for you.

DOWNLOAD A COPY OF THE CIRRUS LOGIC BLU-RAY DISC® PLAYER/RECEIVER SOLUTIONS BROCHURE AT WWW.CIRRUS.COM/4353EDN

**NORTH AMERICA** +1 800-625-4084

CS4353

Thermally Enhanced

4 mm x 4 mm

QFN Package

(shown at actual size)

ASIA PACIFIC

+852 2376-0801 JAPAN

+81 (3) 5226-7757

**EUROPE/UK** +44 (0) 1628-891-300

## LEARN MORE AT

© 2009 Cirrus Logic, Inc. All rights reserved. Cirrus Logic, Cirrus and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brands and product names may be trademarks or service marks of their respective owners.

Authorized Distributor for more than 400 Supplier Partners.

#### www.digikey.com 1.800.344.4539

\*Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2009 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

## Speaking of porting

This software-porting hands-on experiment uncovers a potential audio decoder for embeddedsystem applications, adding audio or speech to the applications' user interfaces. by Robert Cravotta, Technical Editor

## EDN 8.6.09 contents

#### Ambient-light sensors pack in features to help applications get smarter, greener

1 3 Ambient-light sensors help smartphones conserve display power and improve battery runtime. Newer versions combine improved features, such as spectral response and dynamic range, integrated proximity, and digital communications.

> by Margery Conner, Technical Editor

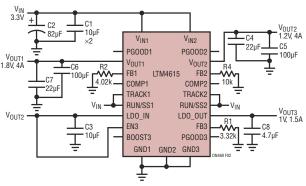

- 6 6A PSIP dc/dc converter achieves 15W/cm<sup>2</sup>

- 6 Monolithic 6A dc/dc stepdown controller integrates synchronous switcher, poweroutput FETs

- 7 Cascade Microtech addresses power semiconductors and RFICs

- 8 Start-up offers dynamically reconfigurable logic technology

- 8 Adjustment-free units simplify precise probe positioning

- 9 Research Update: Iron particle in nanotube may offer archival storage; Cyborg crickets could create cooperative community networks

## DESIGNIDEAS

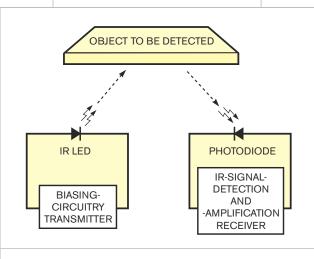

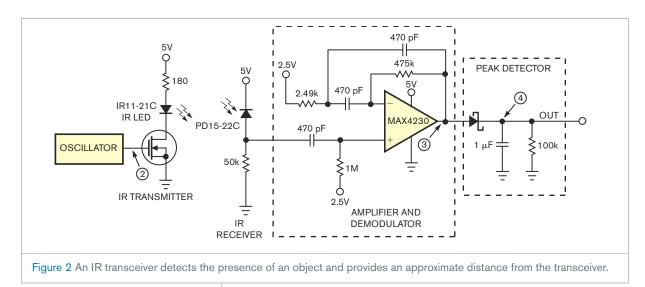

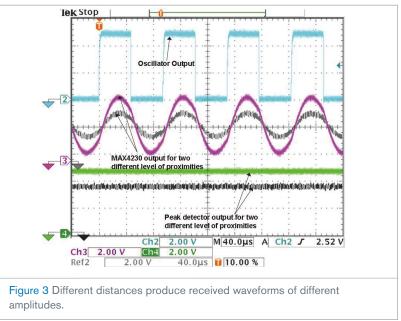

43 High-speed op amp enables IR-proximity sensing

- 44 Set your lights to music

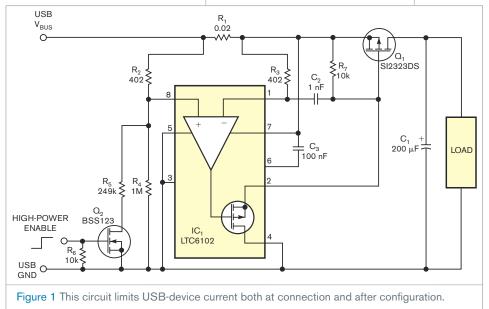

- 48 Current limiter allows large USB bypass capacitance

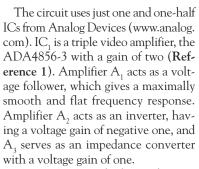

- 50 High-speed pulse modulator retains signal envelope

## IMS highlights student ingenuity

25 Competitions drive student interest in microwave theory and techniquies. *by Jennifer Kempe, Contributing Editor*

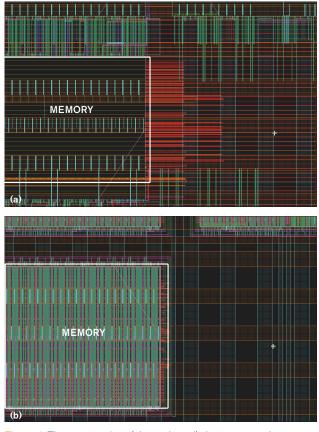

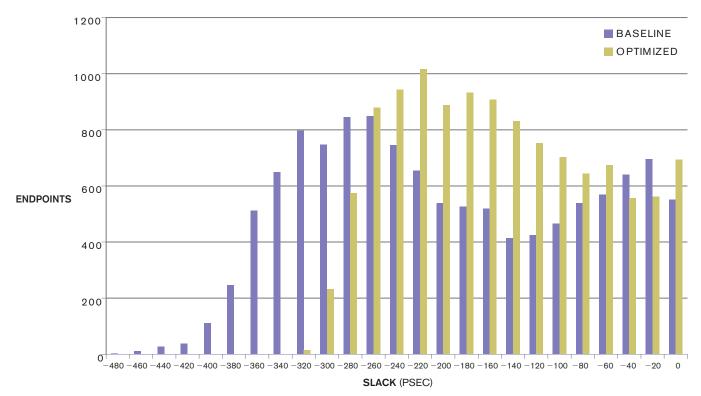

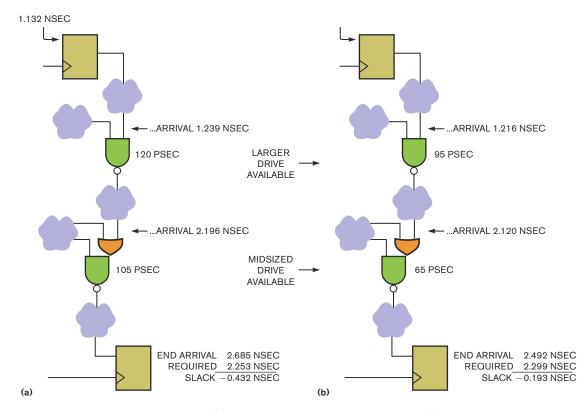

#### Techniques for implementing high-performance processor cores

28 Every step of the integrasign team opportunities to move closer to its design goals. by Gregory Schulte and

Vamsi Boppana

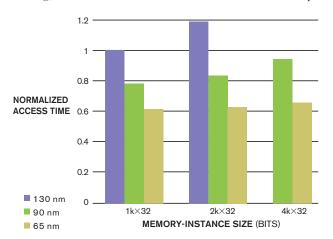

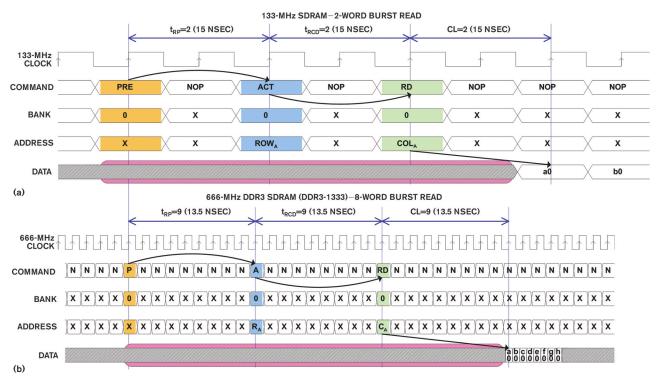

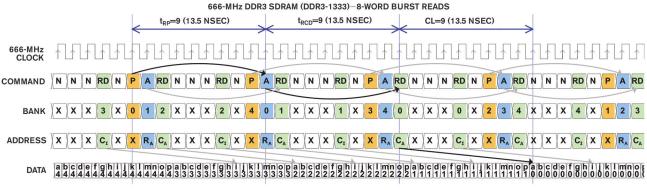

#### DRAM technology for SOC designers and-maybe-their customers

34 An understanding of DRAM technology has become critical to anyone designing consumer-electronics SOCs. by Drew E Wingard, PhD, Sonics Inc

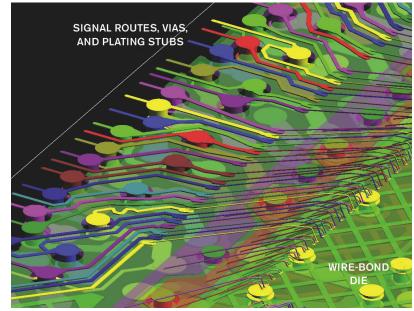

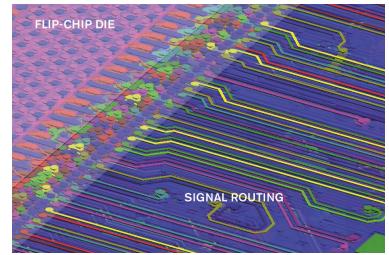

## First-pass success in silicon packaging

**38** Package issues interact with all aspects of the design flow, from chip architecture to manufacturing decisions. *by Javier DeLaCruz, eSilicon Corp*

#### **DEPARTMENTS & COLUMNS**

- 5 EDN.comment: Self-serving "synergy"

- Signal Integrity: The nature of ESD 10

- 54 **Supply Chain:** Job board targets distributors; PC market to slump 6% in 2009; Possible changes to toxic substances control act echo ROHS

- 56 Product Roundup: Discrete Semiconductors, Computers and Peripherals

- 58 Tales from the Cube: Dark side of the light

#### **EDN** online contents

www.edn.com

#### ONLINE ONLY

Check out these Web-exclusive articles:

#### Closing the ESL gap

Plenty of commentary has been written about the promise of ESL and how it remains unfulfilled. The truth is that engineers have been successfully designing with ESL tools for years.

→www.edn.com/article/CA6665045

#### Tackling formal assumptions through verification planning

There are many tools for tracking assertions during verification, but what about the assumptions the design team has made about the design's environment? They need tracking, too.

→www.edn.com/article/CA6669411

**ENGINEERS' TRUE STORIES** Tales from the Cube, which appears on the last page of every issue, has become one of EDN's most popular sections. In EDN's Tales from the Cube, engineers relate their most vexing design challenges-and how they conquered them. From the cubicle to the test bench to the field, hear how your peers solve real-world problems. To catch up on any Tales you might have missed-and to learn how to submit your own-please check out our Tales archive page. →www.edn.com/tales

EDN @ (ISSN#0012-7515), (GST#123397457) is published biweekly, 24 times per year, by Reed Business Information, 8878 Barrons Blvd, Highl Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer: Mark Finkelstein, President, Boston Division, Periodicals postage paid at Littleton, CO 80126 and additional mailing offic es. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN ®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN ® copyright 2009 by Reed Elsev Inc. Rates for nonqualified subscriptions, including all issues: US, \$179.99 one year; Canada, \$229.99 one year (includes 7% GST, GST#123397457); Mexico, \$229.99 one year; air expedited, \$399.99 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign, Publications Agreement No. 40685520, Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N9A 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN ®, 8878 S Barrons Blvd Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 54, Number 15 (Printed in USA).

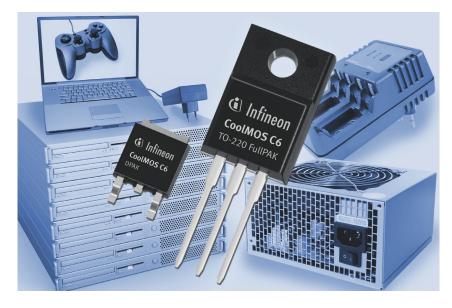

## **Benchmark MOSFETs**

| Number            | (V) | (mΩ) | (nc) | (A) |

|-------------------|-----|------|------|-----|

| IRFP4004PBF       | 40  | 1.70 | 220  | 195 |

| IRFP4368PBF       | 75  | 1.85 | 380  | 195 |

| IRFP4468PBF       | 100 | 2.60 | 360  | 195 |

| IRFP4568PBF       | 150 | 5.90 | 151  | 171 |

| IRFP4668PBF       | 200 | 9.70 | 161  | 130 |

| * Package limited |     |      |      |     |

#### Features

- Suited for Synchronous rectification, active ORing, industrial battery and DC to AC inverters

- Industrial grade and MSL1

- Lead free, RoHS compliant

our

For more information call 1.800.981.8699 or visit

for Performance

International **IOR** Rectifier THE POWER MANAGEMENT LEADER

#### Surface Mount (Thru-Hole Available) (Thransformers and Inductors

See Pico's full Catalog immediately www.picoelectronics.com

#### Low Profile from

#### Audio Transformers Impedance Levels 10 ohms to 250k ohms, Power Levels to 3 Watts, Frequency Response ±3db 20Hz to 250Hz. All units manufactured and tested to MIL-PRF-27. QPL Units available.

Power & EMI Inductors Ideal for noise, spike and Power Filtering Applications in Power Supplies, DC-DC Converters and Switching Regulators

Pulse Transformers 10 Nanoseconds to 100 Microseconds. ET Rating to 150 Volt Microsecond, Manufactured and tested to MIL-PRF-21038.

#### Multiplex Data Bus Pulse Transformers

Plug-In units meet the requirements of QPL-MIL-PRF 21038/27. Surface units are electrical equivilents of QPL-MIL-PRF 21038/27.

#### **DC-DC Converter**

Transformers Input voltages of 5V, 12V, 24V And 48V. Standard Output Voltages to 300V (Special voltages can be supplied). Can be used as self saturating or linear switching applications. All units manufactured and tested to MIL-PRF-27.

#### 400Hz/800Hz Power Transform

**Power Transformers** 0.4 Watts to 150 Watts. Secondary Voltages 5V to 300V. Units manufactured to MIL-PRF-27 Grade 5, Class S (Class V, 155°C available).

Delivery-stock to one week for sample quantities

sample quarter or send direct for FREE PICO Catalog Call toll free 800-431-1064

in NY call **914-738-1400** Fax **914-738-8225**

143 Sparks Ave. Pelham, N.Y. 10803 E Mail: info@picoelectronics.com www.picoelectronics.com

PRESIDENT, BOSTON DIVISION, REED BUSINESS INFORMATION

Mark Finkelstein, mark.finkelstein@reedbusiness.com 1-781-734-8431

#### PUBLISHER, EDN WORLDWIDE

Russell E Pratt 1-781-734-8417; rpratt@reedbusiness.com

ASSOCIATE PUBLISHER, EDN WORLDWIDE Judy Hayes 1-925-736-7617; judy.hayes@reedbusiness.com

VICE PRESIDENT, EDITORIAL DIRECTOR Karen Field 1-781-734-8188; kfield@reedbusiness.com

EDITOR-IN-CHIEF, EDN WORLDWIDE Rick Nelson 1-781-734-8418; rnelson@reedbusiness.com

EXECUTIVE EDITOR Ron Wilson 1-510-744-1263; ronald.wilson@reedbusiness.com

MANAGING EDITOR Amy Norcross 1-781-734-8436; fax: 1-720-356-9161; amy.norcross@reedbusiness.com Contact for contributed technical articles

SENIOR ART DIRECTOR Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

ANALOG Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com

#### MASS STORAGE, MULTIMEDIA, PCs,

AND PERIPHERALS Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com

MICROPROCESSORS, DSPs, AND TOOLS Robert Cravotta, Technical Editor

1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com

NEWS Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com

#### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

#### DESIGN IDEAS EDITOR

Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@reedbusiness.com SENIOR ASSOCIATE EDITOR

Frances T Granville 1-781-734-8439; fax: 1-303-265-3131; f.granville@reedbusiness.com

EDITORIAL/WEB PRODUCTION Diane Malone Manager 1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney Production/Editorial Coordinator 1-781-734-8442; fax: 1-303-265-3198 Melissa Annand Newsletter/Editorial Coordinator 1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi Prepress Manager

1-781-734-8325; fax: 1-303-265-3042 **CONSULTING EDITOR** Jim Williams, Staff Scientist, Linear Technology

CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap

PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Joshua S Levin-Epstein, Production Manager 1-781-734-8333; fax: 1-781-734-8096

EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

EDN ASIA

Luke Rattigan, Chief Executive Officer luke.rattigan@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn Jeff Lu, Executive Editor jefflu@rbichina.com.cn

EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax 1-303-470-4280; subsmail@ reedbusiness.com. For a free subscription, go to www.geffreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

#### BY BRIAN DIPERT, SENIOR TECHNICAL EDITOR

#### Self-serving "synergy"

he HDMI (high-definition-multimedia-interface) organization finalized its Version 1.4 specification in early June. Silicon Image, an HDMI-founder company, subsequently released its first two Version 1.4-supportive chips, the SiI9387 port processor and the SiI9334 transmitter. This timing wasn't the way things were supposed to play out. The original plan was for HDMI to publicly unveil the finalized specification, and Silicon Image to coincidentally unveil the chips, in late April.

Then, the two pushed out the embargo date for both spec and silicon to mid-May and eventually released the spec stand-alone as a two-step preview-then-final introduction, with the chips following it. Despite the multiple delays, nobody else that I know of had as of mid-July released HDMI Version 1.4-supportive chips.

Besides Silicon Image, the other HDMI-founding companies are Hitachi, Matsushita/Panasonic, Philips Consumer Electronics International, Sony, Thomson (RCA), and Toshiba. Although some of these companies have semiconductor divisions, only Silicon Image is fundamentally a semiconductor supplier. And, as a founder, it is in the unique position unlike other HDMI-silicon vendorsof having not only access to proprietary draft versions of upcoming spec revisions, but also the ability to heavily influence the development direction of those spec revisions.

Silicon Image can start its chip-design work early, and the company garners revenue from other silicon suppliers, its supposed competitors, in the form of licensing royalties. And it has yet another notable competitionsquelching arrow in its quiver. Silicon Image is an umbrella organization

## Silicon Image is trying to have it both ways.

comprising three business groups, one of which is Simplay Labs, which handles industrywide compatibility testing. Each Simplay Labs validation attempt costs other companies many thousands of dollars. The validation process also takes as long as Simplay Labs deems it should take. This arrangement gives Silicon Image a convenient lock on the market through the initial and profitable portion of each HDMI specification version's lifetime.

Not surprisingly, I've heard plenty of complaints over the years from companies that try to compete with Silicon Image on the supposedly level global-standard playing field. I've also been on the receiving end of a lot of grumbling from Silicon Image's customers-some of them even on the HDMI founders list! System suppliers would prefer to be able to source products from multiple vendors as a means of obtaining both optimum prices and assured supply. However, again and again, they find that Silicon Image is their only product option in the early stages of an HDMI-specification version. And, by the time an HDMI generation is sufficiently mature that other vendors are available, it's time for Silicon Image's reluctant customers to begin designing systems complying with the next HDMI version.

The market situation is so distorted that a collective of graphics-chip companies and display manufacturers a few years ago developed a competitive interface, DisplayPort. I've suggested many times that DisplayPort's success will be muted at best, in no small part because it took the technology's developers so long to finalize the specification. Meanwhile, HDMI was cultivating an insurmountable lead, especially in consumers' living rooms. Looking at the market today, I see no evidence that my past prognostication was offbase. However, that HDMI's detractors were motivated to spend a substantial amount of money and allocate precious resources for DisplayPort development indicates the industry's aggravation with Silicon Image's de facto HDMI dictatorship.

Silicon Image is trying to have it both ways—painting a picture of HDMI as a cozy, cooperative industry standard, when in reality HDMI is predominantly a single-silicon-supplier proprietary approach.EDN

Contact me at bdipert@edn.com.

+ For more information, go to www.edn.com/blog/400000040/ post/1850046185.html.

+ Read a response from Silicon Image at www.edn.com/090806ed.

#### EDITED BY FRAN GRANVILLE

#### **INNOVATIONS & INNOVATORS**

#### 6A PSIP dc/dc converter achieves 15W/cm<sup>2</sup>

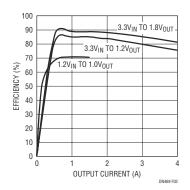

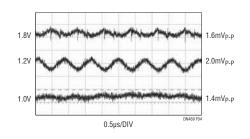

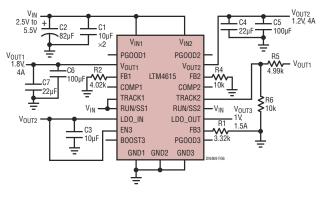

npirion keeps raising the bar on its tiny PSIP (power-supply-in-package) dc/dc buck converters. The 6A EN5364QI and the 9A EN5394QI each have an inputvoltage range of 2.375 to 6.6V and fit into an 8×11×1.85-mm package, achieving as much as 93% efficiency and a power density of 15W/cm<sup>2</sup>. An external resistor divider sets the

Requiring as few as seven external resistors and capacitors, the 6A EN5364QI achieves 15W/cm<sup>2</sup> and efficiency as high as 93%.

output voltage to any user-defined value. The device has an operating frequency of 4 MHz and can synchronize with an external system clock or another EN5364/94.

Like other Enpirion PSIP products, the EN5364/94s integrate power switches, an inductor, a gate drive, a controller, and loop compensation in the 190-mm<sup>2</sup> package, re-

quiring as few as seven external resistors and capacitors. The EN5364 and EN5394 sell for \$6.10 and \$7.50 (1000), respectively.

These figures emphasize the continuing trend toward lower prices and increased power density in the PSIP market. For example, the company about a year ago introduced the \$8.10 (1000), 9A EN5395OI PSIP converter, which fits into a  $10 \times 12 \times 1.85$ -mm package and achieves approximately  $11W/cm^2$ , also with as much as 93% efficiency.

**Enpirion**, www.enpirion.com.

-by Margery Conner

FEEDBACK LOOP "If I were asked about the future of analog, I'd say you're going to have some very large (in terms of functionality onboard) chips, with large application departments at those companies explaining what the chips do and how their customers can use them."

--Design engineer Chris Gammell, in *EDN*'s Feedback Loop, at www.edn.com/article/ CA6666235. Add your comments.

## Monolithic 6A dc/dc step-down controller integrates synchronous switcher, power-output FETs

Texas Instruments' latest additions to its Swift series of powersupply ICs include point-of-load dc/dc converters in highly integrated packages. The 17V TPS54620 step-down synchronous switcher with integrated FETs comes in a  $3.5 \times 3.5$ -mm package and contains the control IC and power-output FETs. After adding a handful of passive components, you can pack a complete 6A power device into less than 195 mm<sup>2</sup>.

Unlike some vendors' approaches to the problem, TI's package hosts a monolithic device with integrated 26-m $\Omega$  high-side and 19-m $\Omega$  low-side FETs. It downconverts supplies ranging from 1.6 to 17V, although you must provide a separate supply of at least 4.5V for control and gate-drive purposes. The inductor sets the height,

or profile, of your converter design; TI's suggested parts list's smallest suitable inductor has a 3-mm profile. The device operates at 200 kHz to 1.6 MHz, and you can lock its switching frequency to an external clock. You must provide an external compensation network of approximately five passive components, and TI's online or downloadable software package, SwitcherPro, assists with calculating those component values. The chip has a 0.8V reference and yields a 1%-accurate output across its range. Peak efficiency is 95%, and the chip maintains better-than-90% efficiency over an output range of 1 to 6A when deriving 3.3V from a 12V input. The TPS54620 costs \$1.95 (1000).—by Graham Prophet **Texas Instruments**, www.ti.com.

#### Cascade Microtech addresses power semiconductors and RFICs

ascade Microtech is addressing the emerging energy-efficiency standards that are driving the need for accurate power-device characterization in automotive, mobile-device, transportation, and other applications. In addition, the company is targeting probing for millimeter-wave RFICs that will serve WirelessHD, automotive radar. and other applications operating in the 60- to 80-GHz range.

In the company's most recent initiative to address power-characterization needs, it introduced a set of probes and accessories for its Tesla on-wafer powerdevice characterization system, making Tesla fully compatible with the recently released Agilent (www.agilent. com) B1505A powerdevice analyzer (see "Tesla power-semiconductor-characterization system debuts," Test & Measurement World, May 29, 2007, www.tmworld. com/article/CA6446837). The combined system offers an extended triaxial measurement range to accommodate low-noise probing of power devices with voltages as high as 2000V.

The award-winning Tesla

#### **DILBERT By Scott Adams**

system meets these demands for making measurements at increasing voltage and current levels when characterizing devices fabricated using new wide-bandgap materials, such as silicon carbide and gallium nitride. Tesla offers what the company says is the industry's highest voltage and current range for on-wafer measurements: as much as 2000V triaxial or 3000V coaxial and as much as 60A pulsed or 20A continu-

ous. With

Using a combination of Cascade Microtech's proprietary thin-film technology and coaxial-probe technology from its Infinity Probe architecture, the 110-GHz Unity-MW RFIC-engineering probe supports the precision characterization and testing of these emerging multiple-port technologies.

Agilent's B1505A power-device analyzer, the new Tesla probes take advantage of the performance of the B1505A, meeting the requirements of more advanced device-characterization applications.

"Power devices are prolific in today's semiconductor industry," says Geoff Wild, chief executive officer of Cascade Microtech. "Our customers are constantly striving to improve the efficiency of these critical IC components. The Tesla system facilitates on-wafer CV, IV, and breakdown measurements, which in turn enables faster development cycles at an overall lower cost of test versus packaged test." Unlike other approaches, Wild adds, the system allows users to realize the full potential of their B1505As with the maximum range of voltage, current, and application compatibility.

Cascade Microtech has also announced two products that streamline engineering and production testing of highbandwidth, short-range RFIC devices for WirelessHD, automotive radar, and other 60-GHz wireless applications,

**Market** researchers point to a surge in demand for devices operating in the 60- to 80-GHz ranae.

joining other companies at the June International Microwave Symposium addressing applications in the 60-GHz area (see "Design and test highlights at the microwave show," Test & Measurement World, www.tmworld. com/blog/640000064/post/ 290045629.html). Using a combination of Cascade Microtech's proprietary thin-film technology and coaxial-probe technology from its Infinity Probe architecture, the 110-GHz Unity-MW (millimeterwave) RFIC engineering probe supports the precision characterization and testing of these emerging multiple-port technologies. Using the same membrane technology, the Pyramid-MW 81-GHz production probe card supports the at-speed test of known-good die in high volume.

Cascade cites market researchers' pointing to a surge in demand for devices operating in the 60- to 80-GHz range: ABI Research (www. abiresearch.com) forecasts the installation of 1 million wireless high-definition TVs worldwide by 2012, with double-digit growth rates, and Strategy Analytics (www.strategyanalytics. com) reports that more than 2.3 million cars will have collision-avoidance radar systems, requiring more than 30 million radar sensors, by 2011.

-by Rick Nelson Cascade Microtech, www. cascademicrotech.com

## pulse

## Start-up offers dynamically reconfigurable logic technology

tart-up Akya is offering IP (intellectual property) to allow IC designers to include reconfigurable logic on their ASSPs (applicationspecific standard products) or ASICs (application-specific integrated circuits). The company delivers both reconfigurable-logic fabric and IP blocks to execute commonly required functions on that fabric. Colin Dente, the company's chief executive officer, says that the reconfigurable logic can be a part of a larger chip design or form the basis of a complete IC. Akya calls its technology ART2. The ART2 architecture separates data flow and control logic to simplify design and implementation of reconfigurable structures.

Akya's technology differs from other concepts that companies have marketed as dynamically reconfigurable. "If I could think of another term to describe what we do, I would use it," says Dente, explaining that the architecture is not completely general-purpose, but that the company designed it to be just reconfigurable enough to do what is necessary in applications such as audio/video codecs and communications-signal processing. The company claims that the technology is particularly efficient at DSP functions.

Any engineer familiar with HDL (hardware-descriptionlanguage)-based design can learn how to use the tools, which allow you to design a fabric that targets a specific application. This fabric comprises and draws on an IP library of processing elements. These elements are typically at the level of arithmetic functions

rather than being fine-grained, gate-level elements. To this fabric, you add an address sequencer and a programmable interconnect to yield a set of processing resources that match your design. The design tools then assist you in creating an explicit control flow for the design, and you can change that flow after the silicon becomes final. The reconfigurability materializes under the direction of the control flow. With every clock cycle, you can completely reconfigure the datapath: You specify which action each processing element is to carry out on a cycle-by-cycle basis.

Doing the control programming is somewhat similar to writing code for a processor. However, the device you work with is not a VLIW (very-longinstruction-word) processor. It does not write and read data to and from memory, and the minimal use of such transactions is one of the sources of Akya's claims of very low power usage: "In [silicon] area and power, we are right at the custom-silicon end of the [design] spectrum," Dente says, adding that portable and battery-powered products are targets for the technology. In part due to the architecture's processing efficiency, clock speed is unlikely to be a constraint for most telecommunication or audio/video-processing functions.

Thanks to the technology's reconfigurability, it reduces the risk inherent in IC design, takes half the design time of RTL (register-transferlevel) design, and lets you quickly modify designs without changing the silicon itself. With a reconfigurable block, you might make one mask set that serves for several designs, making a custom IC viable when it otherwise would not be. The company offers a similar argument for the problem of adapting an IC to changing standards.

Akya supports ART2 with a

development kit that features one high-level language for data flow and another for control; the company also provides comprehensive training in the ART2 architecture compiler. ART2 is available now; the first commercial chip incorporating the technology is in development and will be on sale in an end product in 2010.

−by Graham Prophet ►Akya, www.akya.co.uk.

The two-arm N2785A probe positioner provides quick and stable X-Y positioning using a simple lift-and-drop motion to set the probe in place.

Agilent Technologies' four new oscilloscope-probe positioners, the N278xA series, provide quick and stable probe positioning for measurements on PCBs (printed-circuit boards) and other devices that require hands-free probing. Unlike other probe positioners, which require multiple adjustments to lock the probe holder into place, the onearm N2784A positioner and two-arm N2785A positioner need only a lift-and-drop motion. The probe holders' weight-stabilization technique keeps constant pressure at the probing point, holding the probe tip in position even if someone bumps the target board.

The low-cost, easy-touse N2786A XY-axis probe holder for general-purpose probing features an easy-to-use two-legged positioner that needs no controls for adjusting its position. The 3-D N2787A positioner has a flexible, articulated arm that you can quickly set up in a variety of configurations, yet it allows fine probelocation adjustments to achieve a stable contact.

These positioners fit most Agilent passive and active probes and are compatible with many probes from other manufacturers. US prices begin at \$60.—by Dan Strassberg

Agilent Technologies, www.agilent.com/find/ probe\_positioners.

#### **RESEARCH UPDATE**

## Iron particle in nanotube may offer archival storage

Researchers continue to seek out some plausible application for carbon nanotubes. The latest effort, by a team at the University of California–Berkeley, the Lawrence Berkeley National Laboratory, and Pennsylvania State University, has discovered that a multiwall nanotube containing a particle of iron might just be an effective archival storage device. The researchers fabricated the structure in a single step by pyrolysis of ferrocene in argon at high temperatures. The result is a cloud of nanotubes containing iron nanoparticles. The team then deposited the nanotube fragments on a convenient substrate and fabricated contacts at the ends of likely looking nanotubes, creating the experimental vehicle.

Applying a sufficient voltage

across the nanotube causes the iron particle to move because of electromigration. The team discovered that, using only the applied voltage, they could precisely control both the velocity of the particle and its position in the tube. More significant for storage applications, once you remove the high voltage, the particle stays put. If you don't intentionally move it and it is subject only to thermodynamic forces, the researchers estimate, the particle will stay in place for about 1 billion years at room temperature.

Initially, the researchers read the position of the iron particle in the nanotube with an electron microscope. This approach This memory device comprises an iron nanoparticle within a carbon nanotube.

would be somewhat impractical, however, in a large-scale storage system. So they investigated the electrical resistance of the nanotube with respect to the position of the iron particle and discovered that the resistance shows a close link to the position. Hence, measuring the resistance of the nanotube at a voltage low enough to not move the particle provides a nondestructive read-out of the location of the particle. This reading process is sufficiently precise to allow multibit storage within a single nanotube. University of California-

Berkeley, http://berkeley.edu. Lawrence Berkeley National Laboratory, www. Ibl.gov.

Pennsylvania State University, www.psu.edu.

#### CYBORG CRICKETS COULD CREATE COOPERATIVE COMMUNITY NETWORKS

Crickets, cicadas, katydids, and some other insects make noise by beating their wings. More significantly, they can change the pitch of their wing beats and, hence, the frequency of the noise in response to changes in pitch of other nearby insects. Swarms of these insects form peer-to-peer wireless networks that can propagate information at relatively high speed across significant areas-perhaps tens of kilometers.

The insects use this ability for their own inscrutable purposes. At least they did until they encountered Benjamin Epstein, PhD, vice president of special projects at OpCoast, a provider of

Electronically modified crickets would be the nodes in a local-area sensor network.

custom products for networking, modeling and analysis, software and database systems, and security and lawful interception. Epstein had the idea that by wiring electronics into the wing muscles on cicadas he could in principle artificially modulate the wing beats, in effect loading information into the insects' network and watching it propagate. Epstein landed a re-

search contract from the US Department of Defense to explore the feasibility of the idea for creating a living network of battlefield toxic-gas detectors. Other applications include mine safety and survivor detection in natural disasters. The idea is to create a

package of electronics, including a gas sensor, perhaps an audio sensor in case the insect proves uninterested in rebroadcasting a strange signal by itself, a wing-muscle stimulator, a tiny bit of intelligence, and some sort of power supply. This package has to be small enough to be implantable in the insect and to not interfere with its short-term survival. The size issue, Epstein says, was not so much a concern with cicadas, which can be rather large. It does become an issue with more common and smaller insects, such as crickets, which are more desirable hosts because they can thrive in a wider range of climates.

In operation, the electronics payload would be passive until the detector found whatever it was looking for. The package would then stimulate the insect's wing muscles, causing the bug to emit a particular pitch. Presumably, neighboring insects would pick up the new pitch and repeat it.

OpCoast, www.opcoast. com.

SIGNAL INTEGRITY

#### BY HOWARD JOHNSON, PhD

#### The nature of ESD

lex Ching from BJ Pipeline Inspection Services in Canada designs large, complex digital systems. His product incorporates analog, digital-logic, battery, and chassis grounds, which connect at various "single-point connections" using wires,  $100 \cdot k\Omega$  resistors, and TVSDs (transient-voltage-suppression diodes). When he strikes the product with an ESD (electrostatic discharge), errors appear on sensitive internal LVDS (low-voltage-differential-signaling) data lines. Ching

has sprinkled ESD-protection chips throughout the product in a fruitless attempt to control that problem. He says that, when an ESD event activates these protection chips, they are supposed to dump ESD currents into the digital-logic ground. From the digital-logic ground, he assumes that the currents flow through a single-point connection to the battery-ground network and, from there, through the parallel combination of a 100-k $\Omega$ , highvoltage resistor and an SMBJ5.0CA TVSD to the chassis. "Since the ESD-protection chips are so far from the chassis, ESD currents must travel a long distance on the digital-logic ground before passing through the battery ground to the chassis," Ching says. "Is this long ESD current path causing noise on my LVDS logic?"

Ching faces a common problem: In response to various noise issues that have emerged over the life of his product family, engineers have modified the grounding structure, probably several times, resulting in a "confused" grounding architecture. I cannot understand his whole system from this brief description, but I can perhaps discuss the general nature of an ESD transient.

#### ESD transient currents spread far and wide.

ESD is a fast event. As the ESD currents surge through your system, they follow, at each instant, what seems the best path available. If, for example, an ESD transient current reaches a junction of two wires, it splits evenly, half going down each wire, with no regard to where the wires lead. One path may lead to a good ground, whereas the other leads to an open circuit. The current cannot discern the better path to ground without first propagating to the ends of the two pathways. Only then, after considerable time and many reflections pass, do the lowerfrequency elements of the ESD transient begin to recognize what you may think of as the best path to ground.

As a result of this behavior, the single-point ground connections in Ching's product do almost nothing to guide ESD transient currents. Once inside the product, ESD transient currents spread far and wide regardless of any ground jumpers,  $100 \cdot k\Omega$  resistors,

and TVSDs that may exist. For example, ESD currents can easily jump directly from board to board through no connection other than the parasitic capacitance of one system element to another. In other cases, current flowing on one path can, through the action of mutual inductance, easily induce destructive voltages in an unrelated pathway.

To control ESD transient currents, you must design the system so that ESD events have only one clear path to ground at every point. For example, terminating a shielded cable onto a metal-shell connector with 360° shield contact around the connector and between the connector and the metal system chassis provides an adequate means of shunting ESD transients from a cable shield to the chassis. The transients have nowhere else to go.

Although TVSDs do a good job limiting the voltage across their terminals, they do not prevent current transients from entering your system. Once current passes through a TVSD, it must still return to ground. Generally speaking, if you mount the TVSD anywhere on your PCB (printed-circuit board), then you allow ESD current to flow on the PCB, and you may lose the war for that reason alone. The best designs shunt ESD currents back to earth before entering sensitive areas of the product.

Ching needs to properly diagnose his system before making any more changes. An engineer familiar with EMI (electromagnetic interference) can determine precisely where the ESD currents are flowing within the product and then design adequate means of protecting the product. Doug Smith of D.C. Smith Consultants provides some great tips on his Web site, www. emcesd.com, about diagnosing the flow of current from large, fast transient events.EDN

+ www.edn.com/signalintegrity

#### "I need a function generator that generates efficiency, too."

#### Signal quality is just the beginning.

You're facing faster design cycles and more complicated testing protocols. PC connectivity is more critical than ever, too. Agilent function/arbitrary waveform generators help shorten your test times with legendary signal quality and purity — along with state-of-the-art I/O connectivity. Plus they're bench-friendly, rack-able, reliable and easy to use. That's Agilent. That's smart.

#### **Function/Arbitrary Waveform Generator Series**

33210A-10MHz \$1,195\* 33220A-20MHz \$1,860\* 33250A-80MHz \$4,571\*

Add a FREE External Reference worth up to \$495<sup>\*\*</sup> www.agilent.com/find/smartarb

## 160 Megawatts of Green Engineering MEASURE IT – FIX IT

Since 2001, engineers at Siliken Renewable Energy have used the National Instruments graphical system design platform to produce solar panels generating 160 MW of renewable solar energy.

**MEASURE IT** Acquire Present Analyze Design Analyze and Acquire and Present data Design optimized control algorithms measure data extract information with HMIs. from any sensor and systems Web interfaces, with signal or signal and reports processing

FIX IT -

hardware

**Deploy** Deploy to the hardware platform you choose

Siliken Renewable Energy, one of the world's fastest-growing manufacturers of solar panels, trusts NI LabVIEW software for applications ranging from research and development to automated test. Like Siliken, companies around the world implement the NI graphical system design platform to create environmentally friendly products, technologies, and processes. Using modular hardware and flexible software, they are not only testing and measuring existing systems but also creating innovative ways to fix the problems they find.

>> Download the solar power resource kits at ni.com/160

888 293 3091

#### BY MARGERY CONNER • TECHNICAL EDITOR

## AMBIENT-LIGHT SENSORS PACK IN FEATURES TO HELP APPLICATIONS GET SMO

AMBIENT-LIGHT SENSORS HELP SMART-PHONES CONSERVE DISPLAY POWER AND IMPROVE BATTERY RUNTIME. NEWER VER-SIONS COMBINE IMPROVED FEATURES, SUCH AS SPECTRAL RESPONSE AND DYNAMIC RANGE, INTEGRATED PROXIMITY, AND DIGITAL COMMUNICATIONS. THESE FEATURES ARE READYING THE SENSORS FOR USE IN LARGE-SCREEN AND AUTOMOTIVE DISPLAYS AND SOLID-STATE LIGHTING.

> LSs (ambient-light sensors) have been around for years, but they are now seeing increased use due to the success of smartphones, such as Apple's iPhone. The iPhone uses an ALS to reduce power demands and eke out battery life by adjusting the display lighting for ambient-light conditions. The iPhone

also uses a proximity detector, a close cousin of the ALS, to reconfigure itself in response to user actions. Today, smartphones, with their trademark large LCDs, are the main users of ALSs, but future applications can realize energy savings and increased ease of use. For example, a large-screen LCD TV must

adjust its LED backlighting to the ambient light. Similarly, a room with SSL (solid-state-lighting) illumination can change its lighting based on natural lighting or to suit its occupant's mood. Automobile lighting can accommodate day or night driving or reflect the brightness of streetlights, saving power and providing a better user experience.

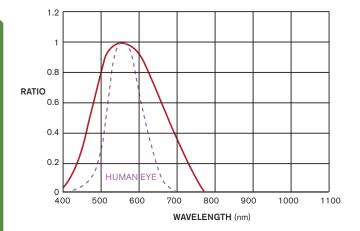

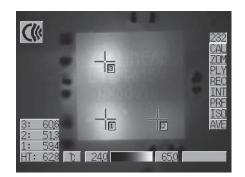

At its most basic, an ALS consists of a photodiode or a phototransistor. However, a simple light-sensitive semiconductor is insufficient because the ALS must be "photopic," meaning sensitive to the same frequency spectrum as the human eye (**Figure 1**). Incandescent and HID (high-intensity-discharge) lights emit 50 to 60% of their radiation in the nonvisible IR (infrared) range as heat. According to Oleg Steciw, product-marketing manager for ALS products at Intersil, you should use the HID with the best spectral response you can find. Otherwise, he says, "You'll be in a

The proximity sensor in a 3G (third-generation) iPhone is within the red circle, and the ambient-light sensor is the green part to its left. The iPhone's speaker is the gray, meshcovered oblong (courtesy iFixit). Light and proximity sensors are often next to a handheld device's speaker because both the sensors and the speaker require access to the outside world. A speaker is a better choice than a microphone because of the humidity that's likely next to a microphone.

room, and, suddenly, the backlight will go haywire because there's some external light source that you can't even see, wreaking havoc."

Werner Mashig, application engineer on Arrow Electronics' lighting team, explains, "[Some] manufacturers put IR-filter [compounds] into the epoxy to filter out the IR light so that the sensor will respond like the human eye."

Another approach is to use multiple photodiodes in the ALS. "One photodi-

ode is a broadband one that sees everything from 300 to 1100 nm," says Carlo Strippoli, vice president of marketing and sales for TAOS (Texas Advanced Optoelectronic Solutions). "The second diode is a dedicated IR photodiode and serves to monitor the IR reaching the sensor and then subtracting it from the light received at the broadband photodiode."

Fluorescent-light sources, which are more efficient than incandescent or HID lights, emit almost none of their radiation in the IR range, but they may exhibit a 60-Hz flicker that can cause an ALS to trigger when it's not supposed to. The newer digital ALSs integrate ADCs that convert the photocurrent to a digital signal to interface to a digital-communication bus. The ADC can serve double duty by filtering out optical noise, such as 60-Hz flicker, through high-resolution sampling. Rohm's BH17xx series integrates a 16-bit ADC that produces 1-lux resolution over a range of 0 to 65.000 lux. Two measurement-resolution levels allow selection between sampling time and performance. In the high-resolution sampling mode, the ADC filters out optical noise. The lower-resolution mode with its shorter sampling time suits applications such as GPSs (global-positioning systems), in which the light-level changes are dynamic: A GPS system will probably operate in an automobile's interior or in natural light. The ideal ALS exhibits uniform light sensitivity regardless of the light source.

"Digital is the direction ambient-light

#### AT A GLANCE

Although smartphones are the major users of ALSs (ambient-light sensors), look for their ability to bring intelligence and power savings to such applications as laptops, TV screens, and automotive and room lighting.

The most important feature for an ALS is its ability to see light as the human eye does. This task requires filtering out the IR (infrared) spectrum.

Solution Vendors are integrating more features, including digital interfaces and proximity sensors, into ALSs.

More complex devices perform RGB (red/green/blue) sensing.

sensing is going," says TAOS' Strippoli. "It allows you to put multiple sensors on a single two-wire bus," such as the I<sup>2</sup>C (inter-integrated circuit). This feature is especially important for flip phones. A digital bus minimizes the number of wires at the hinged interface where the cell phone flips up.

An analog interface requires at least two wires for every sensor. Analog ALSs are still good fits for some designs, such as those in which the voltage or current output of the ALS directly drives the lighting subsystem, those lacking a microcontroller or an available ADC input, and those low-end designs in which price is the dominating feature (Figure 2).

In the past, ALSs could vary from

part to part in the amount of current a given amount of light produces. Such variability makes it difficult to design for a tight sensitivity range. "The manufacturers are [now] doing a great job of binning the components to give more consistency across the design so there's not as much variation of the photocurrent," says Arrow's Mashig. He suggests looking at the specification for photocurrent versus brightness to check the tightness of manufacturers' binning.

A low-power lighting system is especially important for battery-powered devices, and this requirement includes the ALS itself. In general, both analog and digital versions of ALSs have a shutdown or sleep mode, during which the sensor operates at approximately 1  $\mu$ A. Because of the relative simplicity of analog ALSs, they require less power than their digital counterparts. For example, a representative digital ALS draws 190  $\mu$ A in active mode and 1  $\mu$ A in power-down mode due to the integration of the ADC; an analog equivalent of the part draws 97 and 0.4 µA, respectively. However, the total power consumption is comparable to or a little less than that of an analog ALS with a separate ADC.

In addition to an ALS, smartphones often use proximity detectors. Apple's integration of a proximity detector in the iPhone prompted a move toward making handheld consumer devices more intelligent when interacting with their users (see **sidebar** "iPhone puts proximity detection on the map and in your face").

#### **IPHONE PUTS PROXIMITY DETECTION** ON THE MAP AND IN YOUR FACE

The Apple iPhone packs several sensors into its slim profile: an ALS (ambient-light sensor), an accelerometer, and a proximity sensor. In addition, the display itself is a giant touch sensor, and that fact could pose a problem when the phone is in use next to a user's face. Apple solved the problem of inadvertent activation of the screen by including a proximity sensor that detects proximity and turns off the touchscreen when the phone is 3 to 5 cm from a user's face (Reference A).

#### REFERENCE

"iPhone 3G Teardown," www.ifixit.com/ teardown/iphone-3g-s/817/1.

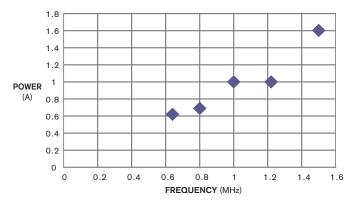

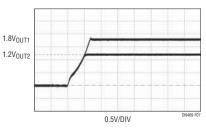

Figure 1 The human eye is sensitive to wavelengths of approximately 380 to 780 nm, peaking at approximately 555 nm. The wider red curve shows the sensitivity of a representative ambient-light sensor.

Because of the close links in both technology and usage between ALSs and proximity detectors, ALS vendors are starting to add proximity detection to the list of integrated features in ALSs. "The ISL29011 drives an external IR LED so that it synchronizes the transmittivity of the LED and then captures the reflection off the object in front of it," says Intersil's Steciw. "You want the sensing range to be within about 3 to 5 cm."

The placement of the IR LED outside the sensor package gives designers more flexibility in where they place the device or what they'll place it behind, says TAOS' Strippoli. "The iPhone puts [the proximity detector] behind a glass that blocks about 95% of visible light," he adds. "So if you use a device that gives you just a [fixed] single output, you get a very low signal."

For discrete proximity sensors, it's still common to keep the IR-radiating

Figure 2 Although digital ALSs are now available, analog sensors are still popular for many applications. Microsemi's Best Eye processing provides a nearly perfect photopic light-wavelengthresponse curve. The sensor output feeds into a wide-dynamic-range compression amplifier that provides accurate resolution over five decades of ambient light. LED inside the sensor package. Avago recently introduced the APDS-9120 proximity sensor, which combines a built-in signal-conditioning IC, an emitter, and a detector into a package that offers both analog- and digitaloutput options. Like Steciw, Strippoli views the powersaving requirements of portable devices driving the trend in packaging proximity detectors along with the ALS but sees it as part of the move toward greener products. He believes that Asian countries in particular are likely to mandate the ability to tell when a viewer is using a large screen or monitor by monitoring proximity.

ALSs in smartphones detect light intensity but provide no information about the color spectrum. A recent development in ALSs is the ability to perform RGB (red/green/blue) sensing, a necessary feature for large-screen LCDs. For the best viewing experience, these

#### TAKING ADVANTAGE OF LIGHT SENSORS WITH MICROCONTROLLERS RUNNING DALI

#### By Bobby Wong, NEC Electronics America Inc

In our energy-conscious world, one simple way to reduce energy consumption is by adjusting office lights to take advantage of the available natural light. Light sensors can operate in multiple locations to detect the amount of naturally occurring ambient light. With the appropriate lighting system, users could accordingly adjust office lights to produce the desired amount of total lighting necessary for each area. Sensors have proved that they can dramatically enhance lighting systems-from improving energy efficiency by sensing ambient light to improving color by detecting light output. Although sensors provide the data, the lighting system still needs an intelligent microcontroller to receive and process the data and adjust the lights accordingly.

However, saving energy should not reduce productivity. A smart microcontroller-based lighting system would allow users to override the automatic light-level sensors when necessary and "remember" programmed user settings to enhance the users' experience.

Although multiarea lighting control, sensor input/processing, and scene setting may sound complicated, the DALI (digital-addressable-lighting-interface) protocol for white-light control in offices and factories already implements many of these features. Companies space these sensors and lights throughout their facilities, and the devices therefore require a network. The DALI network

can control as many as 64 lights with 64 generic controls, such as slider dimmers and sensors. Each area light can store as many as 16 scenes, and each scene stores a digital-dimming level of 0 to 255. When a sensor provides ambient-light input to the microcontroller, the microcontroller can send a DALI command through the network to any of the 64 lights and control them to dim to a specific scene setting. The DALI protocol is also extensible, allowing a supplier to include vendor-specific features for added value. Some microcontrollers have specialized hardware for driving lights from fluorescent tubes to LEDs, and they simplify the support for a DALI network. Unlike discrete light drivers, these microcontrollers can process sensor inputs and intelligently control lights in a wide area using the DALI protocol to produce the optimized amount of light and save energy along the way (Reference A).

#### REFERENCE

Lighting-control solutions," NEC Electronics America, www. am.necel.com/applications/lighting.

#### AUTHOR'S BIOGRAPHY

Bobby Wong is technical-marketing engineer for the multipurpose-microcontroller strategic-business unit at NEC Electronics America Inc. displays must match their backlighting to the color temperature of the ambient lighting (Reference 1). The LCD controller uses the RGB ALS output to tune the RGB HB (high-brightness) LEDs to match the ambient lighting: Backlighting for a fluorescent-lit room has a different color temperature from that of a natural- or incandescent-lit room. In addition, as RGB LEDs age, their color changes slightly, calling for an additional RGB ALS in the backlight itself to sense and give feedback to drive the compensation for the LEDs' color change. Intersil, TAOS, and Rohm all offer RGB sensors.

SSL is an emerging application for RGB ALSs. In this application, color sensors provide feedback to a room's lighting-control system to adjust the light intensity, color, and color-temperature output of the HB LED-based luminaires. Lighting-control information is more complex than the simple on/offlight-switch information that room lighting currently uses, and lighting designers must be familiar with communication protocols. The DALI (digital-addressable-lighting-interface) protocol, which theatrical lighting has used for years, is one possible approach (see **sidebar** "Taking advantage of light sensors with microcontrollers running DALI").

Automotive lighting also needs ALSs. Night-driving applications have for years used simple photosensors to turn lights on and off, but more complex ALSs optimize cabin lighting for safe driving and for aesthetics, such as colored lighting

#### FOR MORE INFORMATION

Apple www.apple.com Arrow Electronics www.arrow.com Avago Technologies www.avagotech.com Intersil www.intersil.com Microsemi www.microsemi.com NEC Electronics www.necel.com Optek www.optek.com

Osram www.osram.com Panasonic pewa.panasonic.com Rohm www.rohm semiconductor.com Sharp www.sharpmeg.com TAOS www.taosinc.com Toshiba www.toshiba.com Vishay www.vishay.com and light-intensity variation. Like most other automotive components, ALS specifications must include operation over the wider temperature and vibration range.EDN

#### REFERENCE

■ Conner, Margery, "The direction of light: Electronic and thermal improvements bring advances to lighting technologies," *EDN*, Feb 5, 2009, pg 26, www.edn.com/article/CA6632368.

+ Go to www.edn.com/090806df1 and click on Feedback Loop to post a comment on this article.

+ For more technical articles, go to www.edn.com/features.

#### You can reach Technical Editor

at 1-805-461-8242 and mconner@ connerbase.com

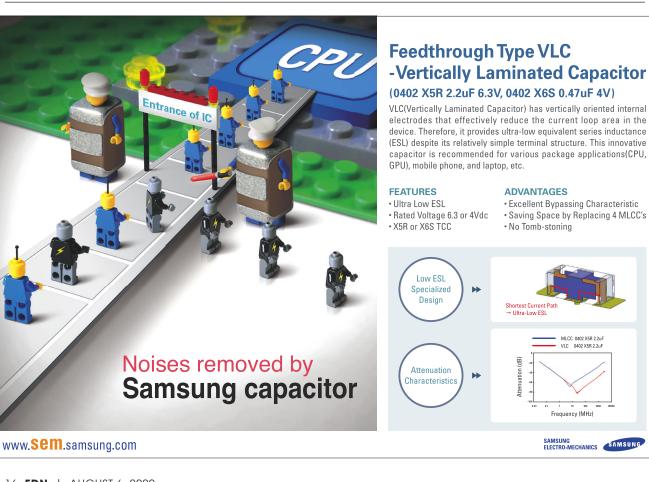

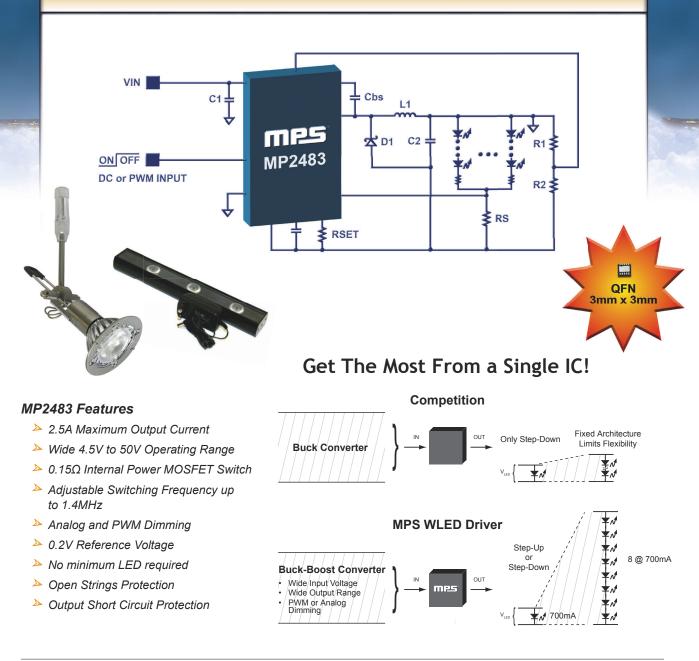

## Drive Up To Eight 700mA LEDs

#### 2.5A, 50V Programmable Frequency White LED Driver

DC to DC Converters CCFL / LED Drivers Class D Audio Amplifiers Linear ICs

## **SPEAKING** OF PORTING SOFTWARE

#### BY ROBERT CRAVOTTA • TECHNICAL EDITOR

he goal of this hands-on project was to port a common set of software across a variety of processor architectures: two ARM Cortex-M3 ports using Atmel and Texas Instruments processors, a port to a Microchip PIC32 device, and a port to an Atmel AVR32 processor. Each port hit some snags, but they all successfully completed the goal of a working port of the

target software. During the project, I realized that the software for the porting effort, Vorbis Tremor, might also make a good candidate for embedded-system developers to consider when exploring how to add audio to their embedded-system design.

I adopted two lessons I learned from a previous project about accelerating software with hardware that spans multiple vendors (**Reference 1**). This project uses a common set of software in each port so that everyone can benefit from identifying the differences and similarities in each effort. The second lesson I learned was to ensure that each vendor provided engineering support so that its development kit can be part of the project. This requirement serves multiple purposes, most notably not overwhelming me with more than 70 development kits.

For these projects, it is imperative to choose a scale of work that is neither too trivial nor too ambitious. An original candidate for the software to port was benchmark code from the EEMBC (Embedded Microprocessor Benchmark Consortium) because many companies use the benchmark software on their processors, meaning that more compaTHIS SOFTWARE-PORTING HANDS-ON EXPERIMENT UNCOV-ERS A POTENTIAL AUDIO DECODER FOR EMBEDDED-SYS-TEM APPLICATIONS, ADDING AUDIO OR SPEECH TO THE APPLICATIONS' USER INTERFACES.

Figure 1 The SAM3U-EK evaluation kit supported the port to Atmel's ARM Cortex-M3 processor.

Figure 2 The ATEVK1105 evaluation kit supported the port to Atmel's AVR32 processor.

nies would be able to participate in the project. However, the focus of the project was on the porting effort rather than the optimization of the code and processor architecture, and these benchmarks focus on the processing performance of the core. For these reasons, I eventually abandoned the idea of using benchmark code in favor of using an audio codec because it combines the requirements for real-time performance with a real-world interface for storage, retrieval, and playback of the audio. I also needed no expensive equipment to tell whether the code was running in real time because I had access to sensitive and free signal processors-my ears-to tell whether the audio was playing too fast or too slow or that the processor was missing data.

While exploring the idea of using an audio codec, including MP3, for the porting target, I discovered the opensource Ogg Vorbis audio-compression format and its Tremor library, a fixedpoint implementation of the Vorbis decoder. Using a fixed-point decoder would allow more processor architectures to participate in this project.

Borrowing from another lesson I learned from my earlier life as an engineer, I framed the project description to avoid as much bias as possible in how each team approached the porting effort (**Reference 2**). This type of uncertainty when specifying a project often yields unexpected benefits, and this project was no exception. The project required the porting effort only to provide

a mechanism to store and access audio files and be able to play them on some output. Each vendor could choose any processor and any development tools it wished to complete the porting effort. Each team made different choices in solving the porting challenge, and one of those design decisions highlighted why the Tremor player might be a good candidate for embedded-system developers to consider.

#### FOUR PORTS

For this project, each engineer was free to select development boards and

#### AT A GLANCE

Contemporary compilers are competent at creating executables of open-source software for embedded-processor targets.

Compilers cannot automate the porting of real-world interfaces and managing dynamic-memory structures. This task remains a vendor's job or a hands-on job.

Embedded development tools must support a complex ecosystem of host and target architectures; this arrangement provides many opportunities for unexpected behaviors to manifest themselves in the tools.

The Tremor audio decoder is a candidate worth considering for embedded-system designers exploring whether to add rich audio data to their interfaces.

tools. The porting effort took an average of a day and a half from choosing the target, understanding the open-source software, and making the necessary changes to the software to complete the port. After that, I duplicated the porting effort over the phone with each team. This approach saved me a lot of time, and it gave me access to the thought process of each person. It also meant that each project was unique rather than a refinement of my own effort with each development kit. In each porting effort, some things worked smoothly, but there was always something that did not proceed the way we would have liked. I will share the hiccups but without specifying with which team it occurred.

Atmel participated in two ports, an AVR32 and an ARM Cortex-M3 (Figure 1). A different team member performed each port, and each took a different approach. The AVR32 port used the ATEVK1105 evaluation kit (Figure 2). Atmel released this new board this year at the ESC (Embedded Systems Conference) in San Jose, CA. We used the AVR32 Studio development-tool set. The audio output went through an adapted DAC for wave playback using software from a previous project that used this peripheral. We performed the port in two stages. The first stage linked the .ogg audio file into the executable file. The second stage accessed the .ogg audio file using code from a FAT (file-allocation-table)-library example through a data-flash device. This two-stage ap-

Figure 3 The Explorer 16 development board supported the port to Microchip's PIC32 processor.

Figure 4 The DK-LM3S9B96 development kit supported the port to Texas Instruments' ARM Cortex-M3 processor.

proach helps isolate delay sources.

The audio codec uses dynamic allocation, which can be a significant source of delay if you are not careful about external-memory accesses and garbage-collection events in the heap. In the case of the AVR device, the multiply function proved to be an area for optimization in part because it handles big- and littleendian representation and it does not take advantage of the extra hardware resources available on the AVR processor to improve multiplication performance.

In addition to isolating sources of delay, this two-stage approach made me realize that I didn't necessarily need to store the audio stream on an external storage device because an embedded system often does not allow the user to access the data, and rarely will it even change the audio stream during the life of the application.

The Atmel ARM Cortex-M3 port used the new SAM3U-EK evaluation kit. This board is so new that a complete set of driver code and samples were unavailable for all of the peripherals, including a DAC driver. The Cortex-M3 is a new generation of the ARM architecture and does not directly benefit from legacy code from earlier architectures, such as the ARM7. However, the support library for this architecture will grow, especially as more M3 devices from a growing list of vendors become available. In a sense, this project was an early adopter of this board and processor (Reference 3). The project used the Yagarto (yet-another-GNU-ARM tool chain). The engineer considered other tool chains, such as IAR, but, due to time constraints with a learning curve involving the allocation library, the engineer used Yagarto. The engineer stored and retrieved the audio file from the SD (secure-digital) card using sample opensource code to manage the file system. Onboard NAND flash could also have stored the audio files.

The Atmel M3 port uses a ring-buffer implementation to feed the DAC/ DMA engine transfer; this approach differs from the ping-pong buffers the other ports used. The ring buffer allows the buffer tuning to adjust not only the buffer size but also the number of buffers to optimize performance by tracking how many of the buffers were full over time. For example, with a 22-kbps sample, a 2-kbyte buffer resulted in 60 to 70% full buffers, whereas a 4-kbyte buffer resulted in less than half the buffers being full. The porting effort progressed starting from 8-kbps samples. This approach exposed efficiency issues in the allocation of memory. The CPU's usage with the 8 kbps was 10%, but usage shot up to 60% at 22 kbps. The higher bit rates caused more access to external memory, which introduced significant delays. Possible optimizations include changing the dynamic-memory allocation code as well as some manual managing of the heap to straddle external and internal memory.

The Microchip PIC32 port used the Explorer 16 development board (Fig-

**ure 3**) with a customized board and the MPlab Real ICE (in-circuit emulator). We used the MPlab Academic version for the software-development tool chain. The PIC32 device is pin-compatible with earlier 16-bit devices and uses the same peripheral blocks as the PIC24. The porting used legacy code by recompiling the PIC24 code. We stored and retrieved the audio files with an SD card and played through the PWM (pulse-width modulator) using a pingpong-buffer implementation.

The Texas Instruments ARM Cortex-M3 port used the DK-LM3S9B96 development kit with the Keil µVision3 software-development tool chain (Figure **4**). This effort required rewriting the allocation routines to avoid dynamic allocation during playback; this task included explicitly defining a stack and a heap space. We stored and retrieved the audio files with the SD card using sample code. The audio output used I2S (inter-IC-sound) demonstration code, which included volume control and a touchscreen scroll interface. Other optimization options would address the multiplication macros.

#### PROBLEMS

Each porting effort ran into problems. Some of these problems were earlyadopter problems, such as when you are using newly released resources. For example, one of the boards had an earlier version of the firmware that had a problem that the manufacturer fixed in a later version of the firmware. From this situation, I learned that there should be a straightforward way to update the firmware or version information on the box to avoid sending out a board with a problem that the manufacturer has already fixed.

To make this project more interesting, I used a 64-bit Vista desktop. None of the original port efforts used this machine, so, although this approach did not stop the projects, it did cause some stalls. In one case, we learned that we had to explicitly install the softwaredevelopment tools as administrators by right-clicking the setup.exe file and specifying "run" as administrators. In two projects, we had trouble with getting my desktop to properly recognize the board through the USB (Universal Serial Bus). In one case, it required finding the 64-bit version of the .inf file in a different directory from the directory in the 32-bit version. In another case, it required adding the missing 64-bit information to the 32-bit version. Apparently, 64-bit Vista has not been a big issue, but I expect that more developers will in the near future be using 64-bit Vista hosts. These types of problems help to illustrate the challenges facing development-tool support teams as they work to support not only several host operating systems, but also different versions of these operating systems.

In one porting effort, the development-tool installation DVD was a blank disk. Fortunately, quickly downloading and online access of all files eliminated that problem, but the problem marred an otherwise-excellent experience with these kits. In another case, the manufacturer had to separately ship a power cord because not all kits included a power cord. The reason for this omission was to help keep the cost of the kits down and to avoid filling your drawers with too many redundant power cords.

A snag occurred when I tried to plug in a serial port between my desktop and the development board. Imagine my surprise when I realized that my computer had a dozen USB ports but no serial port. Two other computers that I recently purchased also had no serial port. You might need a serial port, but do not assume that manufacturers still include them.

Despite all of these problems, the

+ For related blog posts about embedded processing, go to www.edn.com/ blog/1890000189.html.

bring-up on the boards was usually smooth and straightforward. We would set up and power up the board and then verify that the preloaded software was operating properly. After that, we would select some code, compile it in the tool set, load it onto the board, and then verify that it was operating properly. Starting from a known condition and adding one more step into the tool-chain flow in this way helped us identify where a problem might originate and how to address it. Likewise, with the porting effort, adding peripheral ports one at a time or increasing the bit rate in steps helped isolate where logic and performance problems were originating.

#### **NO SILVER BULLET**

In this porting, we had to rewrite the input and output of the audio data. The Vorbis implementation uses stdio for handling the input and output. However, the authors of the software recognize that this mechanism is not appropriate for embedded-system applications, so the code includes a callback structure, ov callbacks, that allows a developer to provide custom functions for these important I/O functions, including decoding a Vorbis stream from a memory buffer.

A big reason for doing this experiment was to demonstrate that there are no silver bullets for porting code—especially embedded code. None of these ports used an operating system on the target system. As a result, accessing the peripherals required an explicit effort by the developer. This effort might include pulling code from a library or from sample code or, in an early-adopter phase, writing the code yourself.

Additionally, the software may exhibit issues depending on how the memory architecture has changed. Unfortunately, compilers are weak in this area and do not provide as much automation or assistance as developers could use. However, Tremor comes in three main versions. A general-purpose implementation targets processors with access to large off-chip memory, a low-memory version trades memory space for more instructions during execution, and a third version contains low-memory code for processors without byte addressing.

The Ogg Vorbis specification is in the public domain and is free for commercial or noncommercial use, making the format an interesting candidate for embedded-system applications. Developers can independently write Ogg Vorbis software that is compatible with the specification for no charge and without restrictions of any kind. As embedded-system applications expand and the richness of the user interface expands beyond blinking lights and simple buzzers, such as those on coffee pots and washing machines, developers may want to consider the Tremor implementation. Embedded systems need not support file sharing that a rich usermultimedia environment might have to do, and they can take advantage of the static nature of the audio messages they might include to provide a new and costeffective differentiating feature. As for choosing a processor and the development-support tools, this exercise demonstrated that vendors that are serious about supporting this capability may want to perform an optimization of the Tremor code and offer it as a referencedesign implementation.EDN

#### REFERENCES

Cravotta, Robert, "Accelerate your performance," *EDN*, Nov 11, 2004, pg 50, www.edn.com/article/CA476908.

Cravotta, Robert, "Valuing uncertainty," *EDN*, Jan 5, 2006, pg 38, www.edn. com/article/CA6294179.

Cravotta, Robert, "Welcome to the jungle," *EDN*, Oct 30, 2003, pg 39, www.edn.com/article/CA330073.

#### FOR MORE INFORMATION

ARM www.arm.com Atmel www.atmel.com EEMBC www.eembc.org IAR www.iar.com Microchip www.microchip.com Texas Instruments www.ti.com Xiph.Org Foundation www.xiph.org

# **RISE ABOVE**

New Xilinx Targeted Design Platforms give designers a boost to take innovation to a much higher level. These comprehensive platforms combine Virtex<sup>®</sup>-6 or Spartan<sup>®</sup>-6 devices, the ISE Design Suite 11, development hardware, IP, reference designs, documentation, and service and support—so you're way ahead of the competition before you even start. Plus, everything works together seamlessly, so design teams can focus on product differentiation, add more value, and make the whole project more successful. Learn more now at www.xilinx.com/6.

# The path of least resistance

**TRANSMISSIO**

www.samtec.com/tls

## ....for high density interfaces.

#### **SEARAY**<sup>TM</sup>

- 500 I/O open pin field array for routing flexibility

- 7mm to 17.5mm stacks, 10.5 GHz in differential configuration

- Low insertion and extraction forces

- Standard and custom jumper lengths and pin counts

#### SEARAY™ Right Angle

Reduced skew and impedance mismatch for micro backplanes

#### HD Mezz™

- Elevated stack heights up to 35mm

- Rated at 9.5 GHz single ended

- Up to 299 I/Os

- HD Mezz is a trademark of Molex Incorporated

#### **DP Array™**

E SOLUTIONS

- Easier differential routing

- Up to 168 pairs, up to 17mm stacks

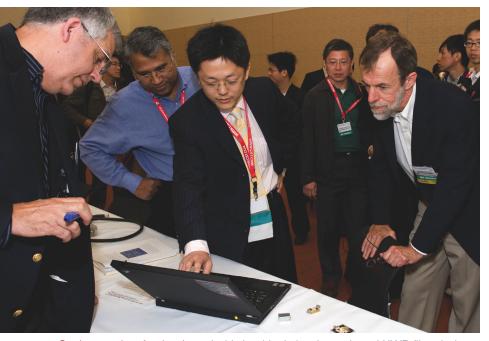

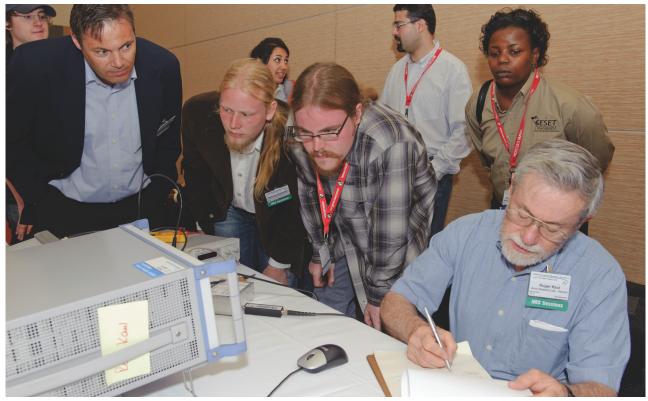

tudents from across the globe gathered at the 2009 IMS (International Microwave Symposium) in Boston June 7 through 12 to demonstrate their innovative approaches to the microwave industry. This year, the IEEE MTT-S (Microwave Theory and Techniques Society), which sponsors the IMS, challenged students to participate in three design competitions, as well as the symposium's traditional student-paper

competition. Each of the events pushed students to work beyond their fundamental training with the technology to create designs that function successfully at a professional level. David Yu-Ting Wu, a student at the University of Waterloo (Waterloo, ON, Canada, uwaterloo/ca), presents his winning prototype for the high-efficiency-power-amplifierdesign competition to a group of MTT-S judges (courtesy MTT-S).

BY JENNIFER KEMPE . CONTRIBUTING EDITOR

## STUDENT NGENUTY

INTEREST IN MICROWAVE THEORY AND TECHNIQUES.

MTT-S organizers say that the student-paper competition is one of the most active segments of the IMS technical program. This year, students-most of them at the graduate level-submitted 235 papers, accounting for 25% of all the submissions to the symposium. The technical-program committee reviewed each paper and judged the submissions based on quantitative content, presentation quality, and MTT-S interest in the subject matter. From all the submissions, the judges selected 24 papers as finalists for presentation at the symposium. Student papers this year addressed topics including reconfigurable microwave filters, millimeter-wave antenna arrays, outphasing transmitters, dielectric-resonator filters, substrate-integrated waveguides, UWB (ultrawideband)-over-fiber systems, power amplifiers, cognitive radio, RF MEMS (radio-frequency microelectromechanical) switches, and implantable medical devices for transcutaneous transmission.

James Komiak of BAE Systems (www. baesystems.com), who volunteers to help organize the student program as a member of the MTT-S technical committee, considers the student-paper competition to be an asset to both the students and the professionals who work with them. "The quality of the student papers has been just amazing in what they're achiev-

#### AT A GLANCE

The student-paper competition at the MTT-S (Microwave Theory and Techniques Society)-sponsored IMS (International Microwave Symposium) benefits both the students and the professionals who work with them.

The first student-design competition aimed to engage students with practical applications of design rather than theory.

This year, the symposium offered competitions for designing a packaged UWB (ultrawideband) filter and a low-noise amplifier.

Nost of the students employed a trial-and-error approach to adjusting their designs to meet the official specifications.

ing on a professional level," he says. "The program allows them to network and make contact with the judges, so it's an important step in their academic and future professional career." The opportunity for professional achievement associated with the paper competition has led to the success of the program, as participation in recent years has grown.

#### **INTEREST IN MICROWAVE**

Although the symposium has offered the student-paper competition

Students and professionals work side by side during the packaged-UWB-filter-design competition at the 2009 IMS (courtesy MTT-S).